ADI AD9164BBCAZ

- Single 16-bit RF DAC with integrated 32-NCO DDS enabling phase coherent fast frequency hopping at 260 ns minimum dwell time

- Direct RF synthesis from DC to 2.5 GHz in baseband mode, DC to 6 GHz in 2x NRZ mode, and 1.5 GHz to 7.5 GHz in Mix-Mode

- 100 MHz SPI with fast hop modes enables agile NCO frequency updates without FPGA-driven sample data changes

- SYSREF input for JESD204B Subclass 1 multi-device synchronization in phased array and multi-channel radar systems

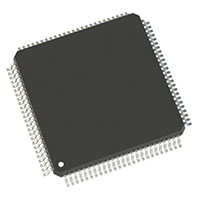

- 169-ball 11mm CSPBGA tape-and-reel package with bypassable 2x to 24x interpolation filters

The ADI AD9164BBCAZ is the tape-and-reel 169-ball 11mm CSPBGA variant of Analog Devices' AD9164, a 16-bit RF DAC and direct digital synthesizer that extends the AD9162 architecture with an integrated bank of 32 independent 32-bit numerically controlled oscillators. Each NCO maintains its own phase accumulator, enabling phase coherent frequency transitions across hops without resetting phase state. When combined with the 100 MHz SPI interface and fast hop modes, the AD9164 supports phase coherent fast frequency hopping with minimum dwell times of 260 ns at the NCO switching speed the FPGA SPI transaction permits. This is the defining capability that separates the AD9164BBCAZ from the AD9162BBCAZ: for radar and electronic warfare programs where frequency agility is a core operational requirement, the integrated DDS eliminates the need for the FPGA to stream new sample data for each frequency hop, dramatically reducing the complexity of the frequency management architecture.

The AD9164 shares the quad-switch DAC core, FIR85 2x interpolation filter, and Mix-Mode reconstruction architecture of the AD9162, providing up to 12 GSPS effective update rate and RF carrier synthesis from 1.5 GHz to 7.5 GHz in Mix-Mode from a 6 GSPS input clock. The SYSREF input, which is exclusive to the BBCAZ variant and not present on the BBCZ tray-packaged device, supports JESD204B Subclass 1 multi-device synchronization for phased array and multi-channel radar systems where deterministic output phase relationships across multiple DAC channels are a system requirement. Bypassable interpolation filters from 2x to 24x allow the FPGA interface data rate to be reduced relative to the DAC sample rate, simplifying the JESD204B link configuration for lower-bandwidth waveforms.

Related Products For Your Business

For radar and electronic warfare transmit chain design, frequency agility is not a nice-to-have feature — it is often the capability that determines whether the system meets its operational requirements. The ADI AD9164BBCAZ brings that agility from the digital domain into the DAC itself. The integrated bank of 32 independent 32-bit NCOs, each with its own phase accumulator and frequency tuning word, means that frequency hops occur at the speed of an SPI write transaction rather than at the rate the FPGA can stream new sample data. At 260 ns minimum dwell time and 100 MHz SPI speed, the AD9164BBCAZ supports frequency hopping rates that cover the full operational requirement of most EW and radar waveform generation applications.

AD9164BBCAZ Architecture: Integrated DDS and Phase Coherent Frequency Hopping

The 32 NCOs in the AD9164’s DDS are pre-loaded with frequency tuning words via SPI at system startup or during configuration. During operation, a single SPI write to the FTW select register switches the active NCO, transitioning the output frequency to the pre-loaded value with deterministic phase relationships between hops. Phase coherent hopping means the phase accumulator of the new NCO continues from a known reference state, not from zero, enabling the receiver to track phase across frequency hops without reacquisition overhead. Three fast hop modes are provided to support different synchronization architectures: single NCO hop, dual NCO hop for ping-pong frequency generation, and a third mode for applications requiring simultaneous multi-frequency synthesis. The SYSREF input, exclusive to the BBCAZ tape-and-reel variant, enables JESD204B Subclass 1 deterministic latency mode for multi-device synchronization across multiple AD9164BBCAZ devices in phased array and multi-channel radar applications where output phase coherence across channels is a system requirement.

AD9164BBCAZ vs AD9162BBCAZ: Choosing Between Streaming DAC and Integrated DDS

The AD9164 and AD9162 share the same quad-switch DAC core, package, and RF output architecture. The integrated DDS is the sole architectural addition in the AD9164:

| AD9164BBCAZ | AD9162BBCAZ | |

|---|---|---|

| DAC Core | 16-bit quad-switch, 12 GSPS effective | 16-bit quad-switch, 12 GSPS effective |

| Integrated DDS | Yes, 32x 32-bit NCOs | No |

| Phase Coherent FFH | Yes, 260 ns min dwell | No (FPGA-driven only) |

| SYSREF Input | Yes (BBCAZ variant) | No |

| Mix-Mode | 1.5 GHz to 7.5 GHz | 1.5 GHz to 7.5 GHz |

| Package | 169-Ball CSPBGA 11mm | 169-Ball CSPBGA 11mm |

| Packaging | Tape and Reel | Tape and Reel |

| Best For | Frequency agile EW and radar, FFH | Static or FPGA-managed frequency synthesis |

Choose the AD9164BBCAZ when frequency hopping speed, phase coherent FFH, or multi-device SYSREF synchronization are system requirements. Choose the AD9162BBCAZ when the waveform synthesis is FPGA-managed and the DDS integration is not needed, accepting a lower system cost. For quad-channel transmit applications at 2.4 GSPS with integrated digital modulation, the AD9154BCPZ is the relevant alternative. For complete transceiver integration with receive ADC cores at 12 GSPS DAC rates, the AD9081BBPZ-4D4AC MxFE addresses that requirement.

Sourcing the ADI AD9164BBCAZ

The AD9164BBCAZ tape-and-reel is the production volume stocking format for the AD9164 in the 11mm CSPBGA package, with demand concentrated in radar and EW programs where the integrated DDS frequency hopping capability is a system requirement. We carry verified inventory with full lot traceability and anti-counterfeit inspection on every order. Contact us today to confirm availability and request a quote, and our team responds within 24 hours.

- 32 pre-loaded NCOs enable SPI-triggered frequency hops without streaming new sample data from the FPGA

- 260 ns minimum dwell time covers the frequency hopping rate requirements of most EW waveform architectures

- SYSREF input exclusive to BBCAZ supports JESD204B Subclass 1 multi-device synchronization in phased arrays

- Phase accumulator continuity across hops enables phase coherent FFH without receiver reacquisition overhead

- Bypassable 2x to 24x interpolation filters allow reduced JESD204B interface data rate for lower-bandwidth waveforms

- IOVDD programmable from 1.8V to 3.3V enables direct connection to FPGA I/O banks without level translators

- AD9164-EBZ and ADS8-V1EBZ evaluation boards support rapid system development and characterization

- Full lot traceability and anti-counterfeit inspection on every order

Frequently Asked Questions (FAQ)

What Is the ADI AD9164BBCAZ and How Does Its DDS Differ From the AD9162BBCAZ?

The AD9164BBCAZ is a 16-bit 12 GSPS RF DAC with an integrated bank of 32 independent 32-bit NCOs providing phase coherent fast frequency hopping at 260 ns minimum dwell time, in a 169-ball 11mm CSPBGA tape-and-reel package. The AD9162BBCAZ uses the same quad-switch DAC core and RF output architecture but without the integrated DDS, requiring the FPGA to manage frequency synthesis by streaming new sample data. The AD9164 is the correct selection when frequency hopping speed and phase coherence are system requirements.

How Does Phase Coherent Fast Frequency Hopping Work on the AD9164BBCAZ?

Each of the 32 NCOs maintains an independent phase accumulator that continues accumulating phase even when the NCO is not selected. When the FTW select register switches the active NCO via SPI, the output transitions to the new frequency with a phase state that reflects the accumulated phase since the NCO was last referenced, not a reset-to-zero state. This phase continuity enables the receiver to track phase coherently across hops without reacquisition time, which is the fundamental requirement for coherent processing of frequency-hopped waveforms in radar and EW applications.

What Is the SYSREF Input and Why Is It Exclusive to the BBCAZ Variant?

SYSREF is a reference signal used in JESD204B Subclass 1 to establish deterministic latency between the DAC and the FPGA data source, enabling multi-device synchronization with known phase relationships. The SYSREF input is present only on the BBCAZ tape-and-reel variant of the AD9164, not on the BBCZ tray variant. For phased array and multi-channel radar designs requiring synchronized output across multiple AD9164BBCAZ devices, the BBCAZ variant must be specified.

What Is the Maximum Junction Temperature Limitation at High Clock Speeds?

At DAC clock speeds above 5.1 GSPS, the maximum junction temperature is limited to 105°C due to elevated power dissipation at high operating frequencies. Below 5.1 GSPS, the standard industrial junction temperature limit applies. System thermal design must ensure the junction temperature remains within specification across all combinations of operating clock speed and ambient temperature.

How Do I Request a Quote for the ADI AD9164BBCAZ?

Submit an inquiry through our website contact form or email our sales team directly. We will respond within 24 hours with pricing, availability, and lead time, and can discuss long-term supply agreements for radar and EW production programs.